Hi all.

SweetAda (https://www.sweetada.org/, GitHub - gabriele-galeotti/SweetAda: Ada-language framework ) “is a lightweight development framework whose purpose is the implementation of Ada-based software systems”.

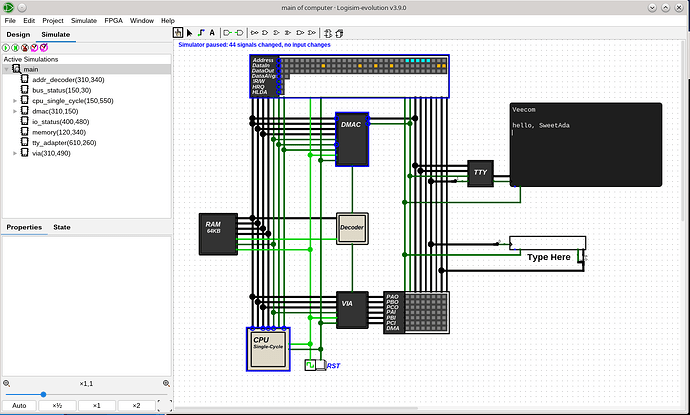

Veecom ( GitHub - Mazin-O3/Veecom: Simple Yet Powerful RISC-V Computer ) “is a 32-bit computer system that combines the simplicity of 8-bit home computers with modern RISC-V technology”. Veecom is a bare digital hardware Logisim-evolution design.

Just for the hardware-cored users, SweetAda, as of commit bbc8ed7, now supports Veecom with no changes to the underlying code base. If you want to see Ada code moving electrons on wires by means of the Logisim simulator, you can try it. Veecom so far lacks exception support, but it simulates an RV32IM CPU, along with a simple DMA controller and a VIA I/O device which interfaces to a TTY console, everything inside the digital simulator.

In order to run SweetAda on Veecom, you need the SRecord package (https://srecord.sourceforge.net/), which converts the final binary code to an srec-compatible format. The target “make postbuild” runs a postbuild.sh script (only *nix, sorry I still do not have so far Logisim on a Wins machine, but creating a .bat should be extremely simple) that generates a suitable memory image. (PS: anyway, I am working in removing the need by using a little Python/Tcl script)

Once the project is loaded inside Logisim, go into the memory block and right-click to load the memory image, then activate clock ticks to start the CPU.

After a long time (depending on your machine power, maybe just a minute), you should be able to see the welcome message on the simulated TTY console.